Kód: 01417773

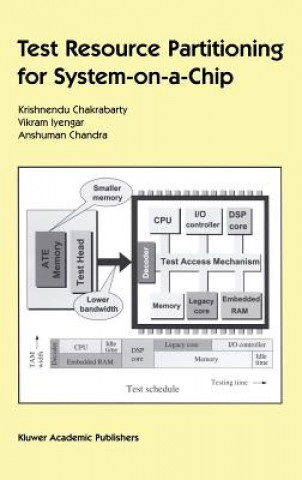

Test Resource Partitioning for System-on-a-Chip

Autor Vikram Iyengar, Anshuman Chandra

Test Resource Partitioning for System-on-a-Chip is about test resource partitioning and optimization techniques for plug-and-play system-on-a-chip (SOC) test automation. Plug-and-play refers to the paradigm in which core-to-core i ... celý popis

- Jazyk:

Angličtina

Angličtina - Väzba: Pevná

- Počet strán: 232

Nakladateľ: Springer-Verlag New York Inc., 2002

- Viac informácií o knihe

139.29 €

Skladom u dodávateľa v malom množstve

Odosielame za 12 - 15 dní

Potrebujete viac kusov?Ak máte záujem o viac kusov, preverte, prosím, najprv dostupnosť titulu na našej zákazníckej podpore.

Pridať medzi želanie

Mohlo by sa vám tiež páčiť

-

Inter-Municipal Cooperation in Europe

139.29 € -

Neurology Self-Assessment: A Companion to Bradley's Neurology in Clinical Practice

71.43 € -

Katy Perry

12.36 € -

Profesor Con Recursos

28.81 € -

Professor and the Madman

19.41 € -25 % -

Maid-sama. Bd.8

6.84 € -9 % -

Moral und Sanktion

48.54 €

Darčekový poukaz: Radosť zaručená

- Darujte poukaz v ľubovoľnej hodnote, a my sa postaráme o zvyšok.

- Poukaz sa vzťahuje na všetky produkty v našej ponuke.

- Elektronický poukaz si vytlačíte z e-mailu a môžete ho ihneď darovať.

- Platnosť poukazu je 12 mesiacov od dátumu vystavenia.

Viac informácií o knihe Test Resource Partitioning for System-on-a-Chip

Nákupom získate 345 bodov

Anotácia knihy

Anotácia knihy

Test Resource Partitioning for System-on-a-Chip is about test resource partitioning and optimization techniques for plug-and-play system-on-a-chip (SOC) test automation. Plug-and-play refers to the paradigm in which core-to-core interfaces as well as core-to-SOC logic interfaces are standardized, such that cores can be easily plugged into "virtual sockets" on the SOC design, and core tests can be plugged into the SOC during test without substantial effort on the part of the system integrator. The goal of the book is to position test resource partitioning in the context of SOC test automation, as well as to generate interest and motivate research on this important topic.§SOC integrated circuits composed of embedded cores are now commonplace. Nevertheless, There remain several roadblocks to rapid and efficient system integration. Test development is seen as a major bottleneck in SOC design, and test challenges are a major contributor to the widening gap between design capability and manufacturing capacity. Testing SOCs is especially challenging in the absence of standardized test structures, test automation tools, and test protocols.§Test Resource Partitioning for System-on-a-Chip responds to a pressing need for a structured methodology for SOC test automation. It presents new techniques for the partitioning and optimization of the three major SOC test resources: test hardware, testing time and test data volume.§Test Resource Partitioning for System-on-a-Chip paves the way for a powerful integrated framework to automate the test flow for a large number of cores in an SOC in a plug-and-play fashion. The framework presented allows the system integrator to reduce test cost and meet short time-to-market requirements.

Parametre knihy

Parametre knihy

Zaradenie knihy Knihy po anglicky Technology, engineering, agriculture Electronics & communications engineering Electronics engineering

139.29 €

- Celý názov: Test Resource Partitioning for System-on-a-Chip

- Autor: Vikram Iyengar, Anshuman Chandra

- Jazyk:

Angličtina

Angličtina - Väzba: Pevná

- Počet strán: 232

- EAN: 9781402071195

- ISBN: 1402071191

- ID: 01417773

- Nakladateľ: Springer-Verlag New York Inc.

- Hmotnosť: 1170 g

- Rozmery: 235 × 155 × 21 mm

- Dátum vydania: 30. June 2002

Obľúbené z iného súdka

-

The Art of Electronics

101.68 € -

Practical Electronics for Inventors

40.05 € -10 % -

The Art of Electronics: The x Chapters

64.89 € -

How to Diagnose and Fix Everything Electronic, Second Edition

24.01 € -17 % -

Electronic Devices, Circuits, and Applications

73.27 € -

Practical Electronics - A Self-Teaching Guide

24.11 € -4 % -

Practical Electronics: A Complete Introduction

18.79 € -19 % -

Lego Power Functions Idea Book, Volume 1

21.96 € -23 % -

Design of Analog CMOS Integrated Circuits

75.82 € -1 % -

Automotive Oscilloscopes

55.69 € -2 % -

Signals & Systems For Dummies

21.15 € -19 % -

LOGO! 8 - A Practical Introduction, with Circuit Solutions and Example Programs

30.55 € -4 % -

LEGO MINDSTORMS EV3 Idea Book

25.03 € -4 % -

Encyclopedia of Electronic Components Volume 2

25.23 € -18 % -

Probabilistic Robotics

117.93 € -11 % -

Motors for Makers

31.47 € -15 % -

Schaum's Outline of Electronic Devices and Circuits, Second Edition

25.64 € -15 % -

High-Frequency Magnetic Components 2e

200.30 € -

Theory of Robot Control

176.80 € -

Introduction to Optimal Control Theory

101.88 € -

Art of Hardware Architecture

139.29 € -

FPGA Design

131.01 € -

Computer Arithmetic

121.40 € -

Schaum's Outline of Digital Principles

36.07 € -

Designing with Xilinx (R) FPGAs

155.74 € -

The LEGO Power Functions Idea Book, Vol. 2

20.33 € -21 % -

Complete Electronics Self-Teaching Guide with Projects

30.24 € -21 % -

Audiophile Vacuum Tube Amplifiers - Design, Construction, Testing, Repairing & Upgrading, Volume 1

72.86 € -

Audiophile Vacuum Tube Amplifiers - Design, Construction, Testing, Repairing & Upgrading, Volume 2

72.86 € -

Audiophile Vacuum Tube Amplifiers Volume 3

72.86 € -

Lego Technic Idea Book: Simple Machines

21.15 € -1 % -

Arduino Cookbook

47.72 € -16 % -

How to Diagnose and Repair Automotive Electrical Systems

27.89 € -11 % -

Electronics For Dummies, UK Edition

28.71 € -5 % -

High Speed Digital Design

99.53 € -

Automobile Electrical and Electronic Systems

70.10 € -

Scary Smart

24.11 € -

3,000 Solved Problems in Electrical Circuits

42.51 € -14 % -

Robotics, Vision and Control

71.53 € -8 % -

Lego Technic Idea Book: Fantastic Contraptions

17.77 € -16 % -

Lego Technic Idea Book: Wheeled Wonders

17.98 € -16 % -

Cybernetics

16.14 € -

Encyclopedia of Electronic Components

20.84 € -20 % -

PLC Controls with Structured Text (ST)

31.98 € -2 % -

Make: More Electronics

28.71 € -20 % -

Fundamentals of Power Electronics

103.93 € -7 % -

Arduino Projects For Dummies

21.96 € -26 % -

C Programming on Raspberry Pi

35.15 € -10 % -

Manga Guide To Microprocessors

22.58 € -14 %

Osobný odber Bratislava a 2642 dalších

Copyright ©2008-24 najlacnejsie-knihy.sk Všetky práva vyhradenéSúkromieCookies

21 miliónov titulov

21 miliónov titulov Vrátenie do mesiaca

Vrátenie do mesiaca 02/210 210 99 (8-15.30h)

02/210 210 99 (8-15.30h)